# Proc10A

## PCIe x8 (Gen. 3) FPGA Computation Accelerators

#### **Key Features**

- Intel Arria 10 (GX660/1100, SX660) FPGA

- PCIe x8 Gen. 3 or stand-alone

- Up to 15×14.2 Gb/s reconfigurable transceivers supporting multiple protocols and data rates

- · Form factor: PCIe half-length

- · Up to 40 GFLOPS-per-Watt

- 1x QSFP, 3x QSFP+ and Gidel highspeed connectors

- Multi-level memory structure (18+ GB)

Sustained throughput of 128+ TB/s for internal memories and ~16 GB/s for on-board memory as follows:

- Enhanced MLAB (640-bit) SRAM blocks

- Up to 2,713 M20K (20K-bit) SRAM blocks (53 Mb) at a typical throughput of 10 TB/s at 450 MHz

- 1 GB DDR3 on-board memory at a maximum sustained throughput of 5.6 GB/s

- 2x16 GB DDR4 ECC SoDIMM Banks for maximum sustained throughput of 19.2 GB/s

- On board user flash (optional)

- Typical system freq: 150-450 MHz

- · Flexible clocking system

- Low power (8-70W)

- Plan to support Gidel's OpenCL BSP and HLS (I++) ASP based on Intel's SDK

- Supported by Gidel's Developer's Kit

- Simultaneous acceleration of multiple applications or processes

- Unmatched HDL design productivity

- Simple integration with software applications

The Proc10A<sup>™</sup> system is a flexible, high-performance, low-power FPGA platform based on Intel's powerful Arria 10 FPGA. The Proc10A's unique architecture balances high performance and flexibility to meet demanding and versatile HPC requirements.

With up to fifteen 14.2 Gb/s full-duplex transceivers and vast memory resources, the Proc10A offers tremendous I/O throughput along with powerful on-board processing and data management capabilities ideal for low latency, high performance HPC, storage, networking, and high-end imaging applications. A multi-level memory scheme includes up to 32 GB DDR3 ECC SODIMM, on-board 1 GB DDR3 SDRAM, dedicated FPGA memory blocks (M20K and MLABs), and other memory options.

In addition, the Proc10A hosts an 8-lane PCI Express Gen. 3 bridge that enables strong co-processing between the host CPU and the FPGA accelerator. For tightly-coupled FPGA and CPU processing, Gidel offers the Proc10A SoC family, with an embedded ARM processor based on the Arria 10 SoC FPGAs.

The Proc10A is supported by Intel's tools and Gidel's innovative development tools, and enables high productivity based on C and HDL designs.

## **Proc10A** - PCIe x8 (Gen. 3) FPGA Computation Accelerators

| FEATURE                | SPECIFICATIONS                                                                   |

|------------------------|----------------------------------------------------------------------------------|

| FPGA                   | Intel Arria 10 GX                                                                |

|                        | • Up to 1150K Logic Elements                                                     |

|                        | Embedded 18x19 Multipliers                                                       |

|                        | Embedded M20K and MLAB blocks                                                    |

|                        | • Up to 15x 12.5/14.1 Gb/s transceivers                                          |

|                        | <ul> <li>1.6 Gb/s LVDS performance</li> </ul>                                    |

| Memory                 | Embedded MLAB (640-bit) SRAM blocks                                              |

|                        | M20K (20K-bit) SRAM blocks                                                       |

|                        | <ul> <li>Up to 32GB DDR4 SDRAM (2x SoDIMMs)</li> </ul>                           |

|                        | On board 2GB DDR4 SDRAM                                                          |

| Processing Performance | <ul> <li>Up to 2,713 M20K blocks @ 450 MT/s for total of<br/>~10 TB/s</li> </ul> |

|                        | MLAB blocks@ 450 MT/s                                                            |

|                        | • Up to 1 GB DDR3 SDRAM for total of 5.6 GB/s                                    |

|                        | • Up to 32 GB DDR3 SDRAM for a total of 19.2 GB/s                                |

|                        | • Up to 3,356 18x19 Variable Precision Multipliers                               |

| MTBF                   | > 1.5 million hours                                                              |

| FEATURE              | SPECIFICATIONS                                                                                                                                 |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Interface       | PCIe x8 Gen.3                                                                                                                                  |

| 1/0                  | 1x, 2x, and 4x SFP+                                                                                                                            |

| GPI0                 | 12x LVTTL                                                                                                                                      |

| Board<br>Management  | Flexible clocking system                                                                                                                       |

|                      | Temperature monitoring                                                                                                                         |

|                      | Internal Voltage monitoring                                                                                                                    |

| Development<br>Tools | OpenCL BSP Based on Intel's SDK                                                                                                                |

|                      | HLS ASP for use with Intel's HLS compiler                                                                                                      |

|                      | • Gidel ProDev Kit for HDL design flow:                                                                                                        |

|                      | <ul> <li>Generation of dedicated application driver.</li> </ul>                                                                                |

|                      | <ul> <li>Splitting of physical on-board memories into<br/>logical memories with independent parallel<br/>access to/from user logic.</li> </ul> |

|                      | <ul> <li>Generation of environment FPGA code,<br/>including all board/IP constrains and user<br/>logic wrapper</li> </ul>                      |

|                      | <ul> <li>Intel Tools: Quartus Prime Pro including QSys and<br/>DSP builder</li> </ul>                                                          |

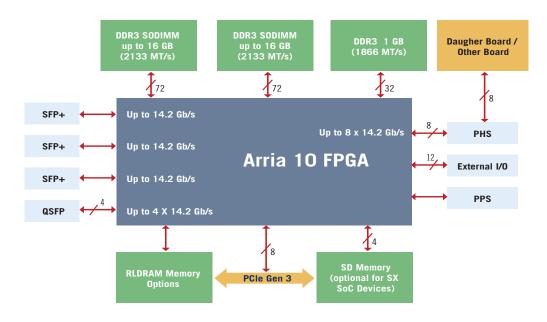

### Proc10A System Block Diagram

2 Ha'ilan St., Northern Ind. Zone POB 281, Or Akiva, Israel 3060000 +972-4-610-2500 sales\_eu@gidel.com